# Design of Two-Rail Checker Using a New Parity Preserving Reversible Logic Gate

Trailokya Nath Sasamal, Ashutosh Kumar Singh, and Anand Mohan

*Abstract*—Reversible logic is one of the basis of future computing system that promises zero energy dissipation. It has applications in various fields such as Low power VLSI, Fault tolerant designs, quantum computing, nanotechnology, DN

A computing, optical computing, cryptography and informatics. To make reversible logic circuits reliable, they must incorporate fault tolerance attribute. In this paper, we propose a new parity preserving reversible logic gate. We have proposed two optimized design of a self checking two rail checker circuit based on proposed parity preserving reversible logic gate in terms of number of gates and critical path delay. The proposed design achieves less critical delay and gates compared to the existing designs available in literature.

*Index Terms*—Critical delay, fault tolerant, parity-preserving reversible gates, two rail checker.

#### I. INTRODUCTION

In the current scenario with increasing complexity in VLSI circuits; managing Power dissipation is an important issue Conventional logic circuits dissipate heat in an order of kTLn2 joules for every bit of information that is lost, where k is the Boltzmann constant and T is the operating temperature [1]. Information is lost when the input vector cannot be uniquely recovered from its output vectors. Reversible logic circuits naturally take care of heating since in a reversible logic every input vector can be uniquely recovered from its output vectors and therefore no information is lost. It has applications in various domain such as Low power VLSI [2], Fault tolerant designs, quantum computing [3], nanotechnology, DNA computing, optical computing [4], cryptography. According to [5], [6] zero energy dissipation would be possible only if the network consists of reversible gates. Thus reversibility will become an essential property in future circuit design. Synthesis of reversible logic circuits differs from the conventional one in many ways. Firstly, in reversible circuit there should be no fan-out, that is, each output will be used only once. Secondly, for each input pattern there should be a unique output pattern. Finally, the resulting circuit must be acyclic. Any reversible gate performs the permutation of its input patterns only and realizes the functions that are reversible. If a reversible gate has k inputs, and therefore k

outputs, then we call it a  $k \times k$  reversible gate. Any reversible circuit design includes only the gates that are reversible. In a reversible circuit, the outputs that are not used as primary outputs are called garbages and the input lines that are set to constants are termed as constant inputs. An efficient design should keep both the number of garbage outputs and constant inputs to minimum.

Fault tolerance is the property that enables a system to continue operating properly in the event of the failure of some its components. If the system itself made of fault tolerant components, then the detection and correction of faults become easier and simple. In communication and many other systems, fault tolerance is achieved by parity. Therefore, parity preserving reversible circuits will be the future design trends towards the development of fault tolerant reversible systems in nanotechnology Rand a gating network will be parity preserving if its individual gate is parity preserving [7]. Thus, we need parity preserving reversible logic gates to construct parity preserving reversible circuits. This paper presents a new parity preserving logic gate that is the parity of the inputs matches the parity of the outputs. Such parity-preserving reversible gates, when used with an arbitrary synthesis strategy for reversible logic circuits, allow any fault that affects no more than a single logic signal to be detectable at the circuit's primary outputs [7]. NPPRG is universal in the sense that it can be used to synthesize any arbitrary Boolean function. For various types of error detection codes self-checking checker must embedded with other testable block. We have also presented two optimised fault tolerant reversible two rail checker using proposed new gate.

The paper is organized as follows: In Section II, basic concepts about reversible gates are introduced. Section III proposes the new parity preserving reversible gate and Section IV shows two designs of two rail checker using proposed new gate. The resulting design is compared to previous work in Section V and the paper is concluded in Section VI.

#### II. REVERSIBLE LOGIC GATES

#### A. Basic Reversible Gates

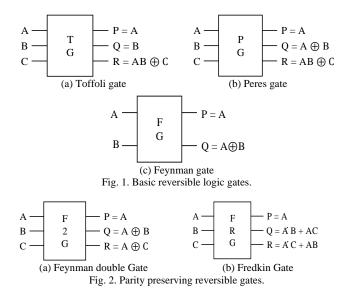

There exist many reversible gates in the literature. Among them  $2\times 2$  Feynman gate (FG) [8], depicted in Fig. 1(a),  $3\times 3$ Peres gate (PG) [9], depicted in Fig. 1(b),  $3\times 3$  Toffoli gate (TG) [10], depicted in Fig. 1(c) and  $3\times 3$  Fredkin gate (FRG) [11], depicted in Fig. 1(d) have been studied extensively.

#### B. Parity Preserving Reversible Gates

Parity checking is one of the most widely used, methods for error detection in digital systems. It's most common use

Manuscript received April 4, 2014; revised July 1, 2014.

Trailokya Nath Sasamal and Anand Mohan are with the Electronics & Communication Department, NIT Kurukshetra-136119, India (e-mail: tnsasamal.ece@nitkkr.ac.in, profanandmohan@gmail.com).

Ashutosh Kumar Singh is with the Department of Computer application, NIT Kurukshetra-136119, India (e-mail: ashutosh@nitkkr.ac.in).

is for detecting errors in the storage or transmission of information, primarily because most arithmetic and other processing functions do not preserve the parity of the data [7]. There have been attempts at performing arithmetic operations on specially encoded operands in a way that parity checking becomes applicable [12], [13]. But the use of traditional methods of error detection in reversible logic, presents some problems, given the requirement for fan-out and the associated increase in "garbage bits", that is, extra bits that are produced to maintain the reversibility property. If computation is performed in such a way that the parity of the input data persists throughout the computation, no intermediate checking would be required. Such results can be forwarded to subsequent modules on the data path, and thus not subject to stringent performance or reversibility requirements. Any erroneous result tends to propagate through the downstream modules without a danger of corrupting additional information in the absence of multiple compensating faults [7]. Given that reversible gates tend to have the same number of input and output lines, a sufficient requirement for parity preservation in the reversible computation, where each gate preserve parity; i.e., have the same parity for input and output lines. More generally, any  $k \times k$  reversible logic gate where the EX-OR of the inputs matches the EX-OR of the outputs will be parity preserving. A few parity preserving logic gates have been proposed in the literature. Among them  $3\times 3$  Feynman Double gate (F2G) [7] depicted in Fig. 2(a) and  $3\times 3$  Fredkin gate (FRG) [11] depicted in Fig. 2(b) are one-through gates, which means one of the inputs is also output. It can be verified from the truth Table I and Table II that the input pattern corresponding to a particular output pattern can be uniquely determined and also satisfying  $A \oplus B \oplus C \oplus D = P \oplus Q \oplus R \oplus S$ so parity-preserving feature holds good.

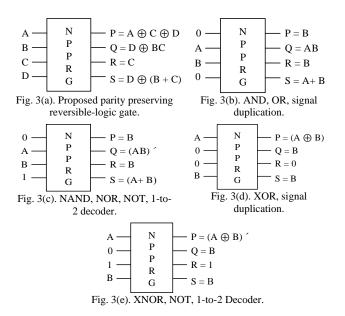

#### III. A NEW PARITY PRESERVING REVERSIBLE GATE

This paper presents a new four-input and four-output reversible-logic gate. The truth table of the gate is shown in Table III. From the truth table, it can be verified that the input pattern corresponding to a particular output pattern can be uniquely determined. The new parity preserving reversible gate, NPPRG shown in Fig. 3(a). The corresponding truth table of the gate is shown in Table III. It can be verified from the truth table that the input pattern corresponding to particular output pattern can be uniquely determined. This is readily verified by comparing the input parity  $A \oplus B \oplus C \oplus D$  to the output parity  $P \oplus Q \oplus R \oplus S$ . The newly proposed NPPRG is universal in the sense that it can be used for implementing arbitrary Boolean functions. The implementation of NPPRG gate as AND, OR function, and signal duplication are shown in Fig. 3(b). The NAND, NOR, NOT function, and 1-to-2 decoder can be simultaneously implemented as shown in Fig. 3(c). The EXOR, EX-NOR functions can be implemented as depicted in Fig. 3(d), and Fig. 3(e) respectively.

TABLE I: TRUTH TABLE OF THE PARITY PRESERVING F2G

| Α | В | С | Р | Q | R |

|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 | 1 |

| 1 | 0 | 0 | 1 | 1 | 1 |

| 1 | 0 | 1 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 | 0 | 0 |

| Α | В | С | Р | Q | R |

|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 | 1 |

| 1 | 0 | 0 | 1 | 0 | 0 |

| 1 | 0 | 1 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 | 1 |

|   |   |   |   |   |   |

TABLE III: TRUTH TABLE OF PROPOSED UNIVERSAL FAULT TOLERANT

| GATE |   |   |   |   |   |   |   |  |

|------|---|---|---|---|---|---|---|--|

| Α    | В | С | D | Р | Q | R | S |  |

| 0    | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |

| 0    | 0 | 0 | 1 | 1 | 1 | 0 | 1 |  |

| 0    | 0 | 1 | 0 | 1 | 0 | 1 | 1 |  |

| 0    | 0 | 1 | 1 | 0 | 1 | 1 | 0 |  |

| 0    | 1 | 0 | 0 | 0 | 0 | 0 | 1 |  |

| 0    | 1 | 0 | 1 | 1 | 1 | 0 | 0 |  |

| 0    | 1 | 1 | 0 | 1 | 1 | 1 | 1 |  |

| 0    | 1 | 1 | 1 | 0 | 0 | 1 | 0 |  |

| 1    | 0 | 0 | 0 | 1 | 0 | 0 | 0 |  |

| 1    | 0 | 0 | 1 | 0 | 1 | 0 | 1 |  |

| 1    | 0 | 1 | 0 | 0 | 0 | 1 | 1 |  |

| 1    | 0 | 1 | 1 | 1 | 1 | 1 | 0 |  |

| 1    | 1 | 0 | 0 | 1 | 0 | 0 | 1 |  |

| 1    | 1 | 0 | 1 | 0 | 1 | 0 | 0 |  |

| 1    | 1 | 1 | 0 | 0 | 1 | 1 | 1 |  |

| 1    | 1 | 1 | 1 | 1 | 0 | 1 | 0 |  |

Proposed parity-preserving reversible gate, satisfying

$A \oplus B \oplus C \oplus D = P \oplus Q \oplus R \oplus S.$

## IV. DESIGN OF TWO RAIL CHECKER BASED ON PARITY PRESERVING REVERSIBLE LOGIC GATES

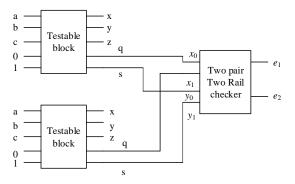

A two rail checker has two groups of inputs  $(x_1, x_2, x_3,...x_n)$  and  $(y_1, y_2, y_3,...y_n)$  and two outputs  $e_1$  and  $e_2$ . The signals observed on the outputs should always be complementary, i.e. a 1-out-of-2 code if and only if every pair  $x_i, y_i$  is also complementary for all  $j (1 \le j \le n)$ .

In a non-error situation when  $x_0x_1 = 11$ ,  $y_0y_1 = 00$ ; the result of this is  $e_1 = 0$ ,  $e_2 = 1$  valid code (Fig. 4(b)). Now consider a situation where due to fault  $y_0y_1 = 10$  output appears 00 or 11 which shows either fault in the checker or at the inputs of the checker. The fault-free checker will produce the complementary outputs if the inputs are complementary. The error checking functions of the two pair rail checker are as follows:

$$e_1 = x_0 y_1 + y_0 x_1$$

$$e_2 = x_0 x_1 + y_0 y_1$$

This two rail checker can be cascaded with testable block [14] The outputs q and s of one testable block forms the input  $x_0$  and  $y_0$  for the two-pair rail checker, and the outputs of another testable block forms the input  $x_1$  and  $y_1$  as shown in Fig. 4(a). Thus, the testable blocks are tested using the two-pair rail checker.

Fig. 4(a). Testable block embedded with the two-pair two-rail checker.

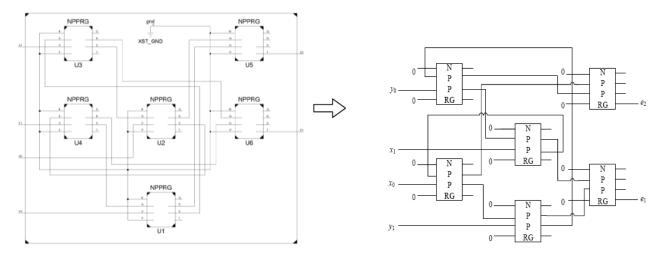

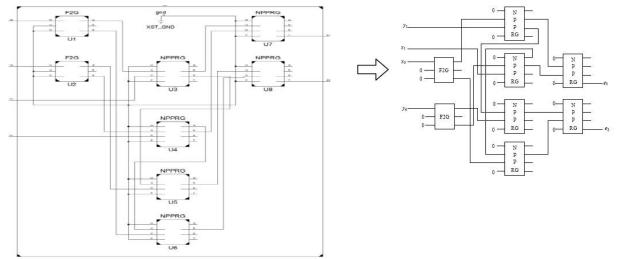

Two designs of two-rail checker is constructed using proposed new gate, as shown in Fig. 5 (a), Fig. 6(a). The first design is composed of eight gates i.e. two F2G and six new gates. The second design is realized with six new gates. Existing two-rail checker has been implemented using eight R gates [14].

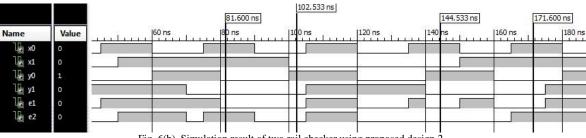

### V. RESULTS AND SIMULATION

A comparison of proposed design with the existing design illustrated in Table V. It shows that the proposed design archives less critical delay as compared with existing design [14]. The proposed parity preserving reversible design 1, design 2 has implemented using 6 and 8 gate respectively, where existing design implemented with 8 gates. The proposed design incorporated with parity preserving feature that enhance fault tolerant attribute, where existing design doesn't have parity preserving feature. The proposed design 2 is more complex but achieves less delay as compared to proposed design 1. All the designs are coded in VHDL for functional verification. The designs are synthesized in Xilinx Virtex-6 FPGA using Xilinx ISE 12.1 for understanding the delay and number of gates [15]. We have created a library of reversible gates in VHDL and used it to code the proposed designs of reversible two rail checker. The functional verification is done using the ISim simulator, which checks the correctness of our proposed designs Fig. 5(b), Fig. 6(b).

| Source                | Destination           | Path delay*             |                      |                      |  |  |  |  |  |  |

|-----------------------|-----------------------|-------------------------|----------------------|----------------------|--|--|--|--|--|--|

| Pad                   | Pad                   | Existing<br>design [15] | Proposed<br>design 1 | Proposed<br>design 2 |  |  |  |  |  |  |

| $x_0$                 | $e_1$                 | 5.216                   | 5.270                | 5.300                |  |  |  |  |  |  |

| <i>x</i> <sub>0</sub> | <i>e</i> <sub>2</sub> | 5.345                   | 5.399                | 5.368                |  |  |  |  |  |  |

| <i>x</i> <sub>1</sub> | <i>e</i> <sub>1</sub> | 5.262                   | 5.349                | 5.378                |  |  |  |  |  |  |

| $x_1$                 | <i>e</i> <sub>2</sub> | 5.391                   | 5.477                | 5.447                |  |  |  |  |  |  |

| <i>y</i> <sub>0</sub> | <i>e</i> <sub>1</sub> | 5.417                   | 5.069                | 5.099                |  |  |  |  |  |  |

| <i>y</i> 0            | <i>e</i> <sub>2</sub> | 5.546                   | 5.198                | 5.167                |  |  |  |  |  |  |

| <i>y</i> <sub>1</sub> | $e_1$                 | 5.415                   | 5.415                | 5.445                |  |  |  |  |  |  |

| <i>y</i> <sub>1</sub> | <i>e</i> <sub>2</sub> | 5.544                   | 5.544                | 5.513                |  |  |  |  |  |  |

TABLE IV: TIMING REPORT

\*All values displayed in nanoseconds (ns).

TABLE V: COMPARISON OF THE PROPOSED DESIGNS WITH EXISTING

| DESIGN                          |                        |                      |                      |  |  |  |  |  |  |

|---------------------------------|------------------------|----------------------|----------------------|--|--|--|--|--|--|

|                                 | Existing<br>design[15] | Proposed<br>design 1 | Proposed<br>design 2 |  |  |  |  |  |  |

| Parity<br>preserving<br>feature | No                     | Yes                  | Yes                  |  |  |  |  |  |  |

| Critical delay                  | 5.546 ns               | 5.544ns              | 5.513ns              |  |  |  |  |  |  |

| Garbage<br>outputs              | 8                      | 6                    | 8                    |  |  |  |  |  |  |

| No. of gates                    | 10                     | 14                   | 18                   |  |  |  |  |  |  |

Fig. 5(a). RTL schematic of proposed design 1 and proposed design 1.

|                   |       | 130.170 ns |       |           |        |        |  |        |       |        |        |            |        |

|-------------------|-------|------------|-------|-----------|--------|--------|--|--------|-------|--------|--------|------------|--------|

|                   |       |            |       | 86.500 ns |        |        |  |        | 154.6 | 40 ns  |        | 188.140 ns |        |

| Name              | Value |            | 80 ns |           | 100 ns | 120 ns |  | 140 ns |       | 160 ns | 180 ns | 2          | 200 ns |

|                   | 0     |            |       |           |        |        |  |        |       |        |        |            |        |

| 1045              | 0     |            |       |           |        |        |  |        |       |        |        |            |        |

| 1015 *            | 0     |            |       |           |        |        |  |        |       |        |        |            |        |

| ી <sub>©</sub> γ1 | 1     |            |       |           |        |        |  |        |       |        |        |            |        |

|                   | 0     |            |       |           |        |        |  |        |       |        |        |            |        |

| le2               | 0     |            |       |           |        | ļ      |  |        |       |        |        |            |        |

Fig. 5(b). Simulation result of two rail checker using proposed design 1.

Fig. 6(a). RTL schematic of proposed design 2 and proposed design 2.

Fig. 6(b). Simulation result of two rail checker using proposed design 2.

# VI. CONCLUSION

A new reversible parity preserving logic gate has been proposed in this paper and presents its universality by implementing all possible Boolean functions. We also presented two designs of reversible fault tolerant two rail checker using the new parity preserving gate with modest hardware overhead. The proposed designs has constructed with the optimum gates and critical path delay. All the designs are functionally verified using VHDL and synthesized using Xilinx Virtex-6 FPGA. The comparative results proved that the proposed designs perform better than the existing design. Proposed reversible checker can be incorporated with various systems to facilitate online error detection. The reduction of garbage outputs using best synthesis algorithm is the primary concern in reversible gate-based design than the actual number of gates for the designers and currently in progress.

#### REFERENCES

- R. Landauer, "Irreversibility and heat generation in the computational process," *IBM J. Research and Development*, vol. 5, pp. 183–191, 1961.

- [2] J. G. Schrom, "Ultra low power CMOS technology," PhD Thesis, Technischen Universitat Wien, June 1998.

- [3] M. A. Nielsen and I. L. Chaung, *Quantum Computation and Quantum Information*, Cambridge University Press, 2000.

- [4] E. Knil, R. Laflamme, and G. J. Milburn, "A scheme for efficient quantum computation with linear optics," *Nature*, pp. 46-52, 2001.

- [5] R. W. Keyes and R. Landauer, "Minimal energy dissipation in logic," *IBM J. Research and Development*, pp. 152-157, March 1970.

- [6] C. Bennett, "Logical reversibility of computation," *IBM Journal of Research and Development*, vol. 17, pp. 525-532, Nov. 1973.

- [7] B. Parhami, "Fault tolerant reversible circuits," in Proc. 40th Asilomar Conf. Signals, Systems, and Computers, October 2006, pp.1726-1729.

- [8] R. Feynman, "Quantum mechanical computers," *Optics News*, vol. 11, pp. 11–20, 1985.

- [9] A. Peres, "Reversible logic and quantum computers," *International Journal on Physical Review a General Physics*, vol. 6, no. 32, pp. 3266–3276, 1985.

- [10] T. Toffoli, "Reversible computing," Tech. Rep. Tech memo MIT/LCS/TM-151, MIT Lab for Computer Science, 1980.

- [11] E. Fredkin and T. Toffoli, "Conservative logic," Intl. Journal of Theoretical Physics, pp. 219-253, 1982.

- [12] B. Parhami, "An approach to the design of parity-checked arithmetic circuits," in *Proc. 36th Asilomar Conf. Signals, Systems, and Computers*, November 2002, pp. 1084-1088.

- [13] B. Parhami, "Parity-Preserving transformations in computer arithmetic," in Proc. SPIE Conf. Advanced Signal Processing Algorithms, Architectures, and Implementations XII, July 2002, pp. 403-411.

- [14] D. P. Vasudevan, P. K. Lala, J. Di and J. P. Parkerson, "Reversiblelogic design with online testability," *IEEE Transactions on Instrumentation and Measurement*, vol. 55, no. 2, April 2006.

- [15] All Programmable Technologies from Xilinx Inc. [Online]. Available: http://direct.xilinx.com/direct/ise6\_tutorials/ise6tut.pdf

**Trailokya Nath Sasamal** received the B.Tech. degree in electronics & telecommunication from the KEC, Bhubaneswar, India, in 2007, and the M.Tech. degree in electronics engineering from Indian Institute of Technology, Banaras Hindu University, Varanasi, India, in 2011. In August 2013, he joined the Electronics & Communication Department, National Institute of Technology, Kurukshetra, India, as an

assistant professor.

His current research interests include reversible logic, fault-tolerant Digital Design and reconfigurable computing.

Ashutosh Kumar Singh received his PhD degree in electronics engineering from Indian Institute of Technology, Banaras Hindu University, India, in 2000. Presently he is working as a professor in the Department of Computer Application, National Institute of Technology, Kurukshetra, India. His research interests include verification curthering dedices and

include verification, synthesis, design, and testing of digital circuits, web technology and teaching & learning. He has published more than 95 research papers to date in different conferences and journals in these areas. He is a co-author of two books named Digital Systems Fundamentals and Computer System Organization and Architecture (Prentice Hall). He has more than 14 years of research and teaching experience in various Universities in India, UK, and Malaysia. He was a member of the editorial board of the University Tun Abdul Razzak (UNITAR) e-journal and has also been involved in the reviewing process of different journals and conferences, such as the IEEE Transactions on Computers, IEEE International Test Conference (ITC), International Conference on Advanced Computing and Communication (ADCOM), and so forth. He is the recipient of the Merit Award from the Institute of Engineers in 2003, the Best Poster Presenter Award from the 86th Indian Science Congress in 1999, and the Best Paper Presenter from the 23rd National Systems Conference (NSC '99) in India.

Anand Mohan is the director of National Institute of Technology (NIT), Kurukshetra. Prior to his present assignment, he was a professor of electronics engineering at Institute of Technology, Banaras Hindu University. He obtained Ph.D., PG, and UG degrees in electronics engineering from Banaras Hindu University in 1994, 1977, and 1973 respectively. His research interests conducted high quality research in the

emerging areas like fault tolerant / survivable system design, information security, and embedded systems involving UG, PG, and Ph.D. students. Prof. Mohan established state-of-the-art research facilities for PG and Research in these areas. In addition, he has made significant contributions to national level research promotion through R & D activities in the area of 'Armament Sensors and Electronics' as Chairman of ASE Panel of DRDO. He has published over 117 research papers in reputed international / national journals and conference proceedings; and supervised large number of Ph. D. theses. He is reviewer of IEEE Transactions on Computer (USA), Journal of Computer and Information Science (Canada), International Journal of Advancements in Computing Technology (Korea), and ET Journal of Institution of Engineers, (India). His research papers have merited awards of International Union of Radio Science (Belgium), Institution of Engineers (India), and Indian Science Congress. His areas of current research interest are information security, fault tolerant design, and programmable logic devices.