# PLC Based Intelligent Toll Road Traffic Control Using

Faraz Islam and Ali Faraz Syed

Abstract—The main object of this paper was to design and implement intelligent toll road traffic control system. The system developed is able to sense the presence or absence of vehicles as the vehicle moves over the LDR (light dependent resister) panels. These LDR panels give their output to the PLC (programmable logic controller). There is a global shift to tolling systems as alternative means of mobilizing domestic revenue for the development and maintenance of road infrastructure. This study examines the effectiveness of toll gate systems. The new timing scheme promises an improvement in the current toll road traffic system and this system is feasible, ready to be implemented and it is also very economical as it uses solar energy from solar panels used for the power consumption.

*Index Terms*—LDR (light dependent resistor), PLC (programmable logic controller), solar panel, toll gate.

# I. INTRODUCTION

Roads arguably are the lifeline of most economies. Fast, reliable roads that efficiently move people and goods are vital for sustaining populations and their economic development. Road transport continues to grow apace, with congestion and bottlenecks affecting an ever growing part of the network. But road infrastructure cannot be extended forever: we need better overall traffic management in order for it to be used to its full capacity. Though toll roads may mitigate infrastructure limitations, they can have diverse impacts on a region's traffic, land use, economy and welfare [1].

An adaptive toll traffic control system must have the ability to diagnose saturation conditions in the network and change the objective function as desired. In older fixed-time systems, there were multiple timing plans, but now a modern toll traffic control system can have multiple control strategies [1].

The Intelligent Toll Road Traffic Control System is an electronic automatism toll collection system that was designed for the highway, bridge and tunnel. Its obvious advantage is of collecting fine from over speeding vehicles and managing traffic on each toll lane.

Vehicles blocked at entrances and exits of toll stations cause huge economic losses when reached a certain threshold. The use of ITRTC system on the highway shows a great potential to solve these problems [2].

When a vehicle comes towards toll station the LDR panels fitted on the highway calculate it's speed and sends the information to PLC.

If it exceeds the speed limit value, then a fine is imposed

Faraz Islam is with the Zakir Hussain College of Engineering and Technology, Aligarh Muslim University, Aligarh, Uttar Pradesh, India (e-mail: fislam2010@gmail.com).

Ali Faraz Syed is with the ACN College of Engineering & Management, Aligarh, M.T.U, Uttar Pradesh, India.

along with the toll tax on the driver. The LDR panel also senses the maximum capacity of the toll lane and if the lane is fully occupied, then the vehicle is directed towards another lane.

#### II. OBJECTIVE

To develop an Intelligent Toll Road Traffic system based on PLC using panels for power supply.

ITRTC simply uses the input module data provided to PLC for safety and traffic management.

# III. METHODOLOGY

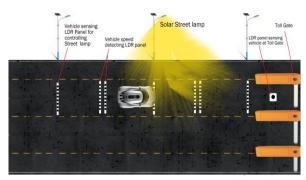

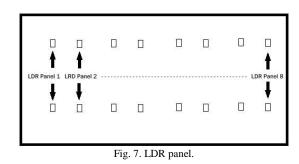

Intelligent toll road traffic control (ITRTC) keeps an eye on over speeding vehicles. ITRTC consists of speed detection LDR panels, these panels are placed on the highway lane and in between two street lamps. Each panel consists of 8 pairs of LDRs. In each pair the LDR is placed one above the other and the distance between the 2 LDRs is 1 meter. When a car moves over the1<sup>st</sup> LDR, and crosses the 2<sup>nd</sup> LDR, the output is send to PLC. From the output provided to PLC, the speed is calculated.

If the speed of the car exceeds the speed limit then the picture of the number plate is captured and sent to PLC for fining process. Now when the car reaches the toll gate the driver has to pay a toll tax and also a fine for over speeding.

Street lamps are powered by solar panels and have sensors below them. These sensors sense the presence of the vehicle as the vehicle crosses the street lamp. The first street lamp switches on by the timer provided to it [1]. As the vehicle crosses the first street lamp, the sensor detects the presence of the vehicle and switches the second street lamp ON. When the vehicle reaches the second street lamp, the first street lamp switches OFF and third lamp switches ON. This process goes on till the end of the toll lane.

Each toll lane of ITRTC consists of LDR panels. When all the LDRs in a particular toll lane detect the presence of a vehicle over them, then they send this output to the PLC. Then the PLC directs the car to another toll lane which is still vacant.

All the input and output modules used in ITRTC is powered by solar energy. Solar panels fitted over the lamps and free space around the ITRTC takes solar energy directly from sun and coverts it into DC power that is stored in heavy batteries [3].

The camera looks after any security breech. It also takes pictures of number plates and sends it to PLC. PLC checks those numbers in registration records for authentication. If a stolen car is found, then the driver is not allowed to pass the

Manuscript received November 10, 2013; revised January 15, 2014.

toll gate and is held for interrogation. The whole setup of ITRTC is solar powered and hence it is economical and eco-friendly. The whole methodology is shown in a sequential manner in Fig. 1.

Fig. 1. Working model of ITRTC.

# IV. PROCESS DESCRIPTION

The chapter gives a detailed explanation of the various processes taking place in Intelligent Toll Road Traffic Control (ITRTC) system. The intelligent toll road traffic control operations are shown in Fig. 2.

Fig. 2. Intelligent Toll Road Traffic Control (ITRTC).

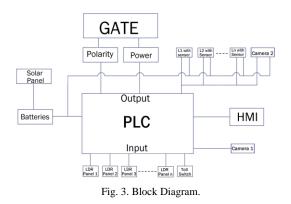

# A. Block Diagram

The basics block diagram (as shown in Fig. 3) of the process and its explanation is given as follows:

# B. Input Module

The input module includes the LDR Panels, Camera and Toll Switch as shown in Fig. 3.

There are N panels of LDR's sensors whose output is given to PLC. The number of panels used in ITRTC depends upon the length of the toll road. The first panel of LDR sensors is used to detect the speed of vehicle.

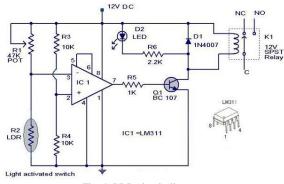

The LDR panel consists of many pairs of LDR's. LDR 1 sense the vehicle which moves over it and as it reaches LDR 2, speed is calculated by the distance travelled by vehicle in respective time. Circuit diagram of a LDR is shown in Fig. 4.

#### Speed = Distance between LDR 1 and LDR 2 Time taken to reach LDR 2 from LDR 1

Cameras are used to capture photos of the vehicle's number plate. This information is given to PLC for checking the authentication of the vehicle registration.

The switch is used to open the toll gate. Gates are controlled by the signal provided by the PLC. If any LDR panel senses an over-speeding vehicle, then the gates are opened by pressing the switch twice, otherwise gates are opened by pressing it only once.

Fig. 4. LDR circuit diagram.

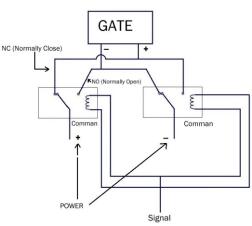

C. Signal Conditioning

Fig. 5. Reverse polarity circuit diagram.

The output of LDR sensors cannot be given directly to the PLC as the input voltage to the PLC should be 24 V. Hence they are given through signal conditioning circuits which condition the input signals and in turn gives it as an input to the PLC. For safety purpose the inputs are not given directly to the PLC. They are given through relay circuits. The relay consists of 3 terminals —common, NO and NC, this circuit is also known as Reverse Polarity Circuit and is shown in (see Fig. 5). The 24 V which is to be pulled into the PLC will be available in the common terminal [4]. Hence depending upon

the necessary signals the circuits closes or opens thereby connecting to the PLC [4].

D. PLC

A Programmable Logic Controller, PLC or Programmable Controller is a digital computer used for automation of electromechanical processes, such as control of machinery on factory assembly lines, amusement rides, or light fixtures [4]. PLCs are used in many industries and machines. Unlike general-purpose computers, the PLC is designed for multiple inputs and output arrangements, extended temperature ranges, immunity to electrical noise and resistance to vibration and impact [5]. Programs to control machine operations are typically stored in battery-backed-up or non-volatile memory.

A PLC is an example of a hard real time system since output results must be produced in response to input conditions within a limited time, otherwise unintended operation will result [6].

The PLC used in ITRTC is SIMATIC S7-300, CPU 316-2DP with integrated 24 V DC power supply, 128 KBYTE working memory 2<sup>nd</sup> INTERF. DP-MASTER/SLAVE.

The details and information of PLC S7-300, CPU 316-2DP is given in Table I [6].

| CPU and Product Version                             |                                     |                                  | S7 timers                                              | 128                       |

|-----------------------------------------------------|-------------------------------------|----------------------------------|--------------------------------------------------------|---------------------------|

| MLFB 6ES57 316-2AG00-0AB0                           |                                     | Adjustable retentivity           | from T 0 to T 127                                      |                           |

| •                                                   | Hardware version                    | 01                               | Preset                                                 | No retentive times        |

| •                                                   | Firmware version                    | V 1.1.0                          | Timing range                                           | 10 ms to 9990 s           |

| •                                                   | Matching programming<br>package     | STEP 7 V 5.0;<br>Service Pack 03 | IEC Timers                                             | Yes                       |

| Memory                                              |                                     |                                  | • Type                                                 | SFB                       |

| Wo                                                  | ork memory                          |                                  | Data areas and their reten                             |                           |

| •                                                   | integral                            | 128 KB                           | Retentive data area as a<br>whole (inc, flags, timers, | 4736 bytes                |

| •                                                   | Expandable                          | no                               | counters)                                              |                           |

| Load memory                                         |                                     | Bit memories                     | 2048                                                   |                           |

| •                                                   | integral                            | 192 KB                           | Adjustable retentivity                                 | MB 0 to MB 255            |

| •                                                   | Expandable FEPROM                   | Up to 4 MB                       | Preset                                                 | MB 0 to MB 17             |

| •                                                   | Expandable RAM                      | no                               | Clock memories                                         | 8 (1 memory byte)         |

| Backup Yes                                          |                                     | Data blocks                      | 511 (DB 0 reserved)                                    |                           |

| •                                                   | With battery                        | All data                         | • Size                                                 | max. 16 KB                |

| •                                                   | Without battery                     | 4736 bytes                       | Adjustable retentivity                                 | max. 8 DB 4096 data bytes |

| Processing times                                    |                                     | Preset                           | No retentivity                                         |                           |

| Processing times for                                |                                     |                                  | Local data (non-alterable)                             | max. 1536 bytes           |

| •                                                   | Bit instructions                    | 0.3 µs minimum                   | <ul> <li>Per priority class</li> </ul>                 | 256 bytes                 |

| •                                                   | Word instructions                   | 1 µs minimum                     | Blocks                                                 |                           |

| •                                                   | Double integer math                 | 2 µs minimum                     | OBs                                                    | See Instruction List      |

| •                                                   | Floating-point math<br>instructions | 50 µs minimum                    | Size     Nesting depth                                 | max. 16 KB                |

| Timers/Counters and their retentive characteristics |                                     |                                  | Per priority class                                     | 8                         |

| <b>S</b> 7                                          | counters                            | 64                               | additional levels within                               | 4                         |

| •                                                   | Adjustable retentivity              | from C 0 to C 63                 | an error OB                                            |                           |

| •                                                   | Preset                              | from C 0 to C 7                  | FBs                                                    | max. 256                  |

| •                                                   | Counting range                      | 0 to 999                         | Size                                                   | max. 16 KB                |

| IEC Counters Yes                                    |                                     | FCs                              | max. 256                                               |                           |

| •                                                   | Type                                | SFB                              | Size                                                   | max. 16 KB                |

#### E. Output Module

The output module includes the Toll Gate, Street Lamp with sensor and Camera.

Toll gates are powered by solar energy and work on the principle of reverse polarity. The driver can open the gate by pressing the gate switch once after paying the toll tax. But if a vehicle breaks the speed limit, then the toll gate opens by pressing the switch twice.

Street lamps are controlled by the output of the LDRs provided to PLC (as shown in Fig. 6). Sensors present on the pole of the street lamp detect the presence of the vehicle as the vehicle crosses the street lamp and switches it on. If no vehicle passes the street lamp, then the lamp remains OFF.

This efficiency of the street lamp provides an efficient way of conserving energy.

Camera provides photo image data of vehicle number plate. This is further processed by PLC for authentication of the vehicle. Cameras increase the security level on highway [7].

Fig. 6. Image of PLC Software used in ITRTC.

# F. Street Lamps Powered by Solar Panels

Solar street lights are raised light sources which are powered by photovoltaic panels mounted on the lighting structure. The photovoltaic panels charge a rechargeable battery, which powers a fluorescent or LED (Light Emitting Diode) lamp during the night [8].

System work is simple, the use of photovoltaic solar cells made of the principle effect of solar panels during the day and to receive solar radiation into electrical energy output [9].

Street lamp used in ITRTC switches ON as a vehicle moves over the LDR panel placed.

#### G. Vehicle Speed Detection Using LDR's

ITRTC consists of speed detection LDR panels (fig 7), these panels are placed on the highway lane in a strip form so that the vehicle can cross the LDR panel and is placed between two street lamps. Each panel consists of 8 pairs of LDR. In each pair the LDR is placed one above the other and the distance between the 2 LDR is 1 meter. When a vehicle moves over 1<sup>st</sup> LDR, and crosses 2<sup>nd</sup> LDR the crossing time as an output is sent to PLC and by the Speed-Distance Formula the Speed is calculated.

# V. CONCLUSION

The main objective of this paper was to develop an

Intelligent Toll Road Traffic Control system based on certain specifications. This was successfully implemented. We considered this paper as a journey where we acquired knowledge and also gained some insight into the subject which we have shared in this report.

A lot of additional features like vehicle detection using sensor, vehicle speed detection using LDR panel and photo monitoring were added in different stages in our work and the desired result were obtained. PLC was used to control various operations and takes input from different devices.

# ACKNOWLEDGMENT

This paper is an outcome of rigorous work done under the supervision and guidance of our research guides. We like to pay our sincere thanks to them, for their kind support and cooperation.

# REFERENCES

- P. Sinhmar, "Intelligent traffic light and density control using IR sensors and microcontroller," *International Journal of Advanced Technology & Engineering Research (IJATER)*, vol. 2, issue 2, Mar. 2012.

- [2] P. M. D. Srivastava, S. Sachin, S. Sharma, and U. Tyagi, "Smart traffic control system using PLC and SCADA," *International Journal of Innovative Research in Science, Engineering and Technology*, vol. 1, issue 2, December 2012.

- [3] H. P Garg and J. Prakash. *Solar Energy: Fundamentals and Applications*, 1<sup>st</sup> ed. Tata McGraw Hill Education, 2012.

- [4] J. R. Hackworth and F. D. Hackworth Jr, "Programmable logic controllers: Programming methods and applications," *Pearson*, 1st ed. 2006, pp. 128-138.

- [5] G. Dunning, P. M. Dunne, and D. R. Anderson, "Introduction to programmable logic controllers," *Delmar*, 3<sup>rd</sup> ed. 2007, pp. 69-81.

- [6] W. Bolton, "Programmable logic controllers," in *Elsevier Science*, 5<sup>th</sup> ed. 2011, pp. 112-124.

- [7] A. Rai and G. S. Patel, "Multiple traffic control using wireless sensor and density measuring camera," *International Frequency Sensors Association (IFSA)*, vol. 94, issue 7, July 2008, pp. 126-132.

- [8] S. P. Sukhatme and J. K. Nayak, Solar Energy: Principles of Thermal Collection and Storage, 3<sup>rd</sup> ed. Tata McGraw - Hill Education, 2008.

- [9] B. H. Khan. Non Conventional Energy Resources, 2<sup>nd</sup> ed. Tata McGraw - Hill Education, 2009, pp. 159-177.

**Faraz Islam** was born in Varanasi, Uttar Pradesh, India on July 8, 1992. He graduated Xth from Our Lady of Fatima, Aligarh, Uttar Pradesh, India in 2008 and XIIth from St. Fidelis, Aligarh, Uttar Pradesh in 2010. Currently he is pursuing computer engineering (3rd year) from Zakir Hussain College of Engineering and Technology, Aligarh Muslim University, Aligarh, Uttar Pradesh, India. He holds a summer training of one month

in Octodi Pvt. Ltd. as of September, 2013. Mr. Islam holds a keen interest in research work and wants to continue pursuing this interest in the field of microprocessors and information technology.

Ali Faraz Syed was born In Aligarh, Uttar Pradesh, India on March 13, 1991. He graduated Xth from S.T.S High School, Aligarh Muslim University, Aligarh, Uttar Pradesh in 2007 and XIIth from Senior Secondary School, Aligarh Muslim University, Aligarh, Uttar Pradesh in 2010. Currently he is pursuing computer engineering (3rd year) from ACN College of Engineering & Management, Aligarh, M.T.U, Uttar Pradesh, India.

He does not hold any word experience as of September, 2013. Mr. Faraz holds a keen interest in research work and wants to continue pursuing this interest in the field of microprocessors and networking.